查看

实现高光提取效率的MicroLED设计

(映维网资讯)在基于MicroLED的显示系统中,从MicroLED阵列发出的光可以准直并耦合到显示器)中,以便将图像传送到输出瞳孔。基于波导的显示系统的总效率Tot可由ηtot=ηEQE×ηin×ηout确定,其中ηEQE为每个MicroLED的外部量子效率EQE,ηin为显示光从MicroLED进入波导的耦入效率。

ηout是显示光从波导到用户眼睛的耦出效率。从LED中提取并由显示光学元件收集的发射光子的比例可称为收集的LEE。对于物理尺寸减小的LED,如MicroLED,其IQEs、收集LEEs和EQEs可能非常低。所以,提高MicroLED的效率可能具有挑战性。

为了改进LEE,特别是所收集的LEE,Meta在名为“Micro-LEDdesignforhighlightextractionefficiency”的专利申请中提出了具有特定结构和宽高比的MicroLED器件。MicroLED器件包括的MicroLED具有半导体平台结构,半导体平台结构包括半导体层,其中半导体平台结构的侧壁可以沿发光方向直、向外倾斜或向内倾斜。

所述MicroLED器件同时可以包括在所述MicroLED的间隔层,以及设置在所述间隔层并配置为提取和准直所述MicroLED发出的光的微透镜。台面结构的横向尺寸可以比微透镜的横向尺寸小得多。例如,微透镜的横向尺寸可等于或大于半导体台面结构的横向尺寸的约1.5、2、3或更多倍,并且因此,MicroLED的发光孔径可相对于微透镜靠近点源。

为了进一步提高MicroLED所收集的LEE,可以选择间隔层的厚度和半导体平台结构的总厚度,使得微透镜的焦点可以位于或接近半导体平台结构的发光表面。例如,间隔层可以具有约为半导体台面结构总厚度的2、3或更多倍的厚度。

在一个实施例中,所述半导体台面结构的总厚度可约为所述MicroLED发出的光的波长。因此,微透镜可以更有效地准直从MicroLED发出的光,并且MicroLED器件的收集LEE可以增加到10%左右。通过改进的结构(例如宽高比),专利描述的MicroLED器件的收集/总LEE比可以增加到约40%,这表明提取的光束具有更好的准直性。

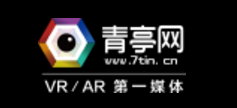

在一个实施例中,为了增加光提取效率,可以形成包括至少一些半导体材料层的台面。图7A示出具有垂直台面结构的LED700的示例。

LED700可以是光源510、540或642中的光发射器。LED700可以是由诸如多层半导体材料等无机材料制成的MicroLED。层状半导体发光器件可包括多层III-V半导体材料。III-V族半导体材料可以包括一种或多种III族元素。

当III-V族半导体材料的V族元素含有氮时,将III-V族半导体材料称为iii-氮化物材料。层状半导体发光器件可以通过使用诸如VPE、LPE、MBE或MOCVD等技术在衬底上生长多个外延层来制造。

在图7A所示的示例中,LED700可以包括衬底710,其可以包括例如蓝宝石衬底或GaN衬底。半导体层720可以生长在衬底710上。半导体层720可以包括III-V材料,例如GaN,并且可以p掺杂)或n掺杂。

可以在半导体层720上生长一个或多个有源层730以形成有源区域。有源层730可包括III-V材料,诸如一个或多个InGaN层、一个或多个AlInGaP层和/或一个或多个GaN层,其可形成一个或多个异质结构,例如一个或多个量子阱或mqw。

半导体层740可以生长在有源层730上。半导体层740可以包括III-V材料,例如GaN,并且可以p掺杂或n掺杂。半导体层720和半导体层740中的一个可以是p型层,另一个可以是n型层。半导体层720和半导体层740夹心有源层730形成发光区。例如,LED700可以包括位于掺杂镁的p型GaN层和掺杂硅或氧的n型GaN层之间的InGaN层。

在一个实施例中,电子阻挡层EBL可以生长成在有源层730和半导体层720或半导体层740中的至少一个之间形成层。它可以降低电子泄漏电流,提高LED的效率。在一个实施例中,可以在半导体层740上形成重掺杂的半导体层750,例如P+或p++半导体层,并作为形成欧姆接触和降低器件的接触阻抗的接触层。

为了与半导体层720接触并更有效地从LED700中提取由有源层730发射的光,可以蚀刻半导体材料层以暴露半导体层720并形成包括层720-760的台面结构。台面结构可将载流子限制在器件内。

蚀刻所述台面结构可导致形成可与所述生长平面正交的台面侧壁732。钝化层770可在台面结构的侧壁732上形成。钝化层770可以包括氧化物层,例如SiO2层,并且可以作为反射器以反射从LED700发出的光。可以在半导体层720上形成接触层780,其可以包括金属层,并且可以作为LED700的电极。另外,可在导电层760上形成另一接触层790,并可作为LED700的另一电极。

当电压信号施加到接触层780和接触层790时,电子和空穴可在有源层730中复合,其中电子和空穴的复合可引起光子发射。所发射光子的波长和能量可取决于有源层730中价带和导带之间的能带隙。

在一个实施例中,LED700可以在诸如衬底710的发光表面上包括一个或多个其他组件,例如透镜,以聚焦或准直发射的光或将发射的光耦合到波导中。在一个实施例中,LED可包括另一形状的台面,例如平面、锥形、半抛物面或抛物面,并且台面的基底面积可为圆形、矩形、六角形或三角形。

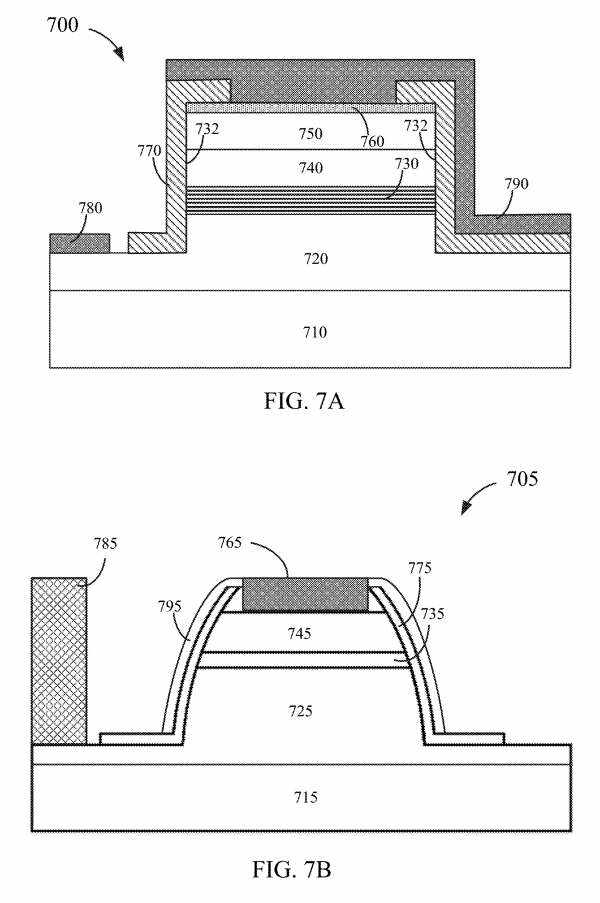

图7B是具有抛物状台面结构的LED705的示例的横截面视图。与LED700类似,LED705可以包括多层半导体材料,例如多层III-V半导体材料。

为了与半导体层725接触并更有效地从LED705中提取由有源层735发射的光,可以蚀刻半导体层以暴露半导体层725并形成包括层725-745的台面结构。台面结构可将载流子限制在器件的注入区域内。

如图7B所示,LED705可以具有包括平顶的台面结构。介电层775可在台面结构的表面上形成。在一个实施例中,介电层775可以包括多层介电材料。可在介电层775上形成金属层795。金属层795可以包括一种或多种金属或金属合金材料。介电层775和金属层795可形成台面反射器,所述反射器可将由有源层735发射的光反射到衬底715。在一个实施例中,台面反射器可以是抛物线形的,以充当可以至少部分准直发射光的抛物线反射器。

可在半导体层745和半导体层725分别形成电触点765和电触点785,以充当电极。电触点765和电触点785均可包括导电材料,并可作为LED705的电极。在图7B所示的实施例中,电触点785可以是n触点,电触点765可以是p触点。电触点765和半导体层745可以形成反向反射器,用于将有源层735发射的光反射回衬底715。

在一个实施例中,电触点765和金属层795包括相同的材料,并且可以使用相同的方法形成。在一个实施例中,可以包括附加导电层,作为电触点765和785与半导体层之间的中间导电层。

当电压信号在触点765和785施加时,电子和空穴可以在有源层735中重新组合。电子和空穴的复合可以引起光子发射,从而产生光。所发射光子的波长和能量可取决于有源层735中价带和导带之间的能带隙。例如,inga活动层可能发出绿色或蓝色光,而AlInGaP活动层可能发出红色、橙色、黄色或绿色光。可以在诸如衬底715的光发射表面形成一个或多个其他次要光学元件,例如透镜或光栅,以聚焦或准直发射的光和/或将发射的光耦合到波导中。

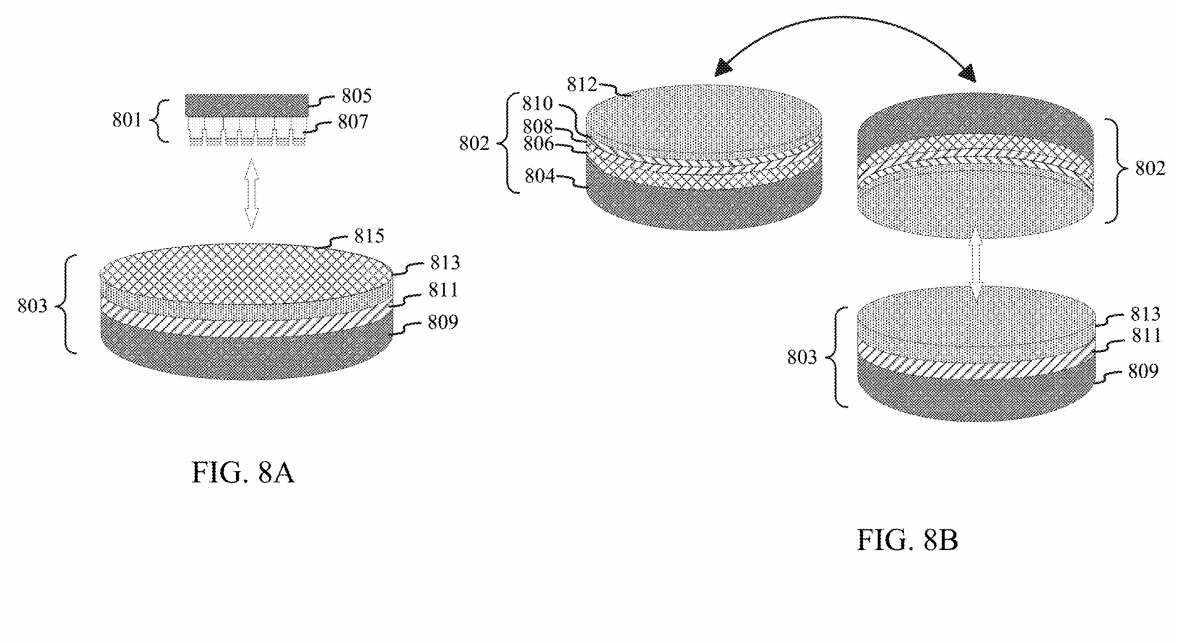

可以在晶圆制造上述LED的一个或二维阵列以形成光源。驱动电路可以在使用CMOS工艺的硅片上制造。晶圆上的LED和驱动电路可以切成小块,然后粘合在一起,或者可以在晶圆级上粘合,然后切割。LED与驱动电路的键合可采用多种键合技术。

图8A示出用于LED阵列的晶圆键合方法。在图8A所示的示例中,LED阵列801可包括载波衬底805上的多个LED807。载流子衬底805可以包括各种材料。在进行键合之前,可以通过例如生长各种外延层、形成台面结构和形成电触点或电极来制造LED807。

晶圆803可以包括具有在其上制造的无源或有源集成电路的基础层809。基础层809可以包括例如硅片。驱动电路811可用于控制LED807的操作。

例如,用于每个LED807的驱动电路可以包括具有两个晶体管和一个电容器的2T1C像素结构。晶圆片803同时可以包括键合层813。键合层813可以包括各种材料。在一个实施例中,可以在键合层813的表面上形成图案化层815。

LED阵列801可通过键合层813或图案层815键合到晶圆803。例如,图案层815可包括由各种材料制成的金属垫或凸起,其可用于将LED阵列801的LED807与晶圆803的相应驱动电路811对齐。

在一个示例中,LED阵列801可以朝向晶圆803,直到LED807与对应于驱动电路811的相应金属衬垫或凸起接触。部分或全部LED807可与驱动电路811对齐,然后可通过各种键合技术键合,通过图图化层815键合到晶圆803。在LED807粘合到晶圆803之后,载流子衬底805可以从LED807移除。

图8B示出用于LED阵列的晶圆到晶圆键合方法。如图8B所示,第一晶圆802可以包括衬底804、第一半导体层806、有源层808和第二半导体层810。衬底804可以包括各种材料。第一半导体层806、有源层808和第二半导体层810可包括各种半导体材料。

在一个实施例中,第一半导体层806可以是n型层,第二半导体层810可以是p型层。例如,第一半导体层806可以是n掺杂的GaN层,第二半导体层810可以是p掺杂的GaN层。有源层808可包括例如一个或多个GaN层、一个或多个InGaN层、一个或多个AlInGaP层等,其可形成一个或多个异质结构,例如一个或多个量子阱或mqw。

在一个实施例中,第一晶圆802可以包括键合层。键合层812可以包括各种材料。在一个示例中,键合层812可以包括p-触点和/或n-触点。其它层可以包括在第一晶圆802,例如衬底804和第一半导体层806之间的缓冲层。缓冲层可以包括各种材料。接触层可位于第二半导体层810和键合层812之间。所述接触层可包括任何用于向第二半导体层810和/或第一半导体层806提供电接触的合适材料。

第一晶圆802可以通过键合层813和/或键合层812键合到包括上述驱动电路811和键合层813的晶圆803。键合层812和键合层813可以由相同的材料或不同的材料制成。键合层813和键合层812可以基本上平坦。第一晶圆802可以通过各种方法键合到晶圆803。

如图8B所示,第一晶圆802可以与第一晶圆802的p面朝下键合到晶圆803。在键合之后,可以从第一晶圆802去除衬底804,然后可以从n面处理第一晶圆802。

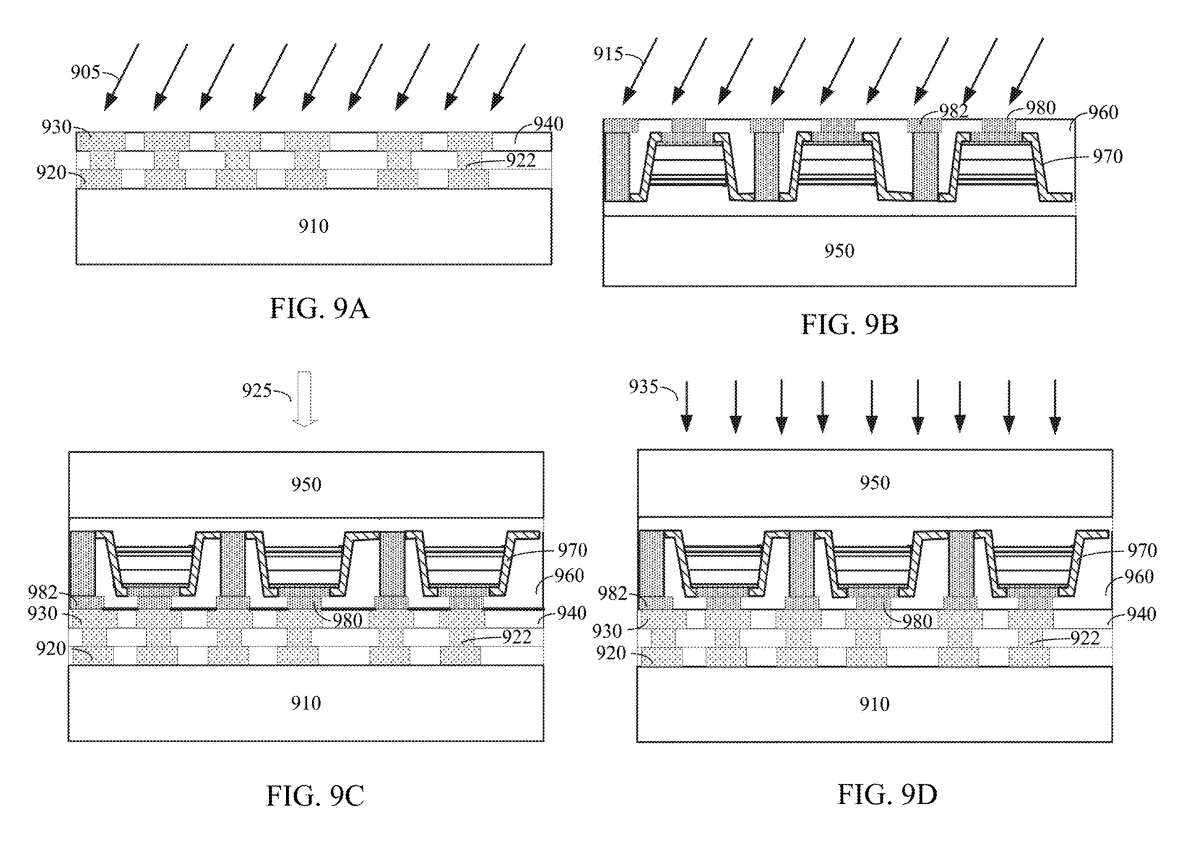

图9A-9D举例说明用于LED阵列的混合键合方法。杂化键合通常可以包括晶圆清洗和活化,一个晶圆的触点与另一个晶圆的触点的高精度对准,在室温下在晶圆表面的介电材料的介电键合,以及通过在高温下退火的触点的金属键合。

图9A示出在其上制造的具有无源或有源电路920的衬底910。电路920可包括用于LED阵列的驱动电路。键合层可包括通过电气互连922连接到电路920的介电区域940和接触垫930。可以通过离子或快原子束905来清洁和激活键合层的表面。

图9B示出了晶圆950。晶圆950可以是载流子晶圆。Micro-LEDs970可包括外延生长在晶圆950上的n型层、有源区和p型层。外延层可以包括上述各种III-V型半导体材料,并且可以从p型层侧加工到在外延层中蚀刻台面结构。可在台面结构的侧壁上形成钝化层和/或反射层。p-触点980和n-触点982可形成于沉积在台面结构上的介电材料层960中,并可分别与p型层和n型层形成电接触。

可以使用例如化学机械抛光使键合层平面化和抛光,其中抛光可能在p触点980和n触点982中造成盘状。然后可以通过例如离子或快原子束915来清洗和激活键合层。

图9C示出用于在键合层中键合介电材料的室温键合过程。例如在包括介电区940和触点垫930的键合层以及包括p-触点980、n-触点982和介电材料层960的键合层被表面激活后,可以将晶圆950和MicroLED970颠倒并使其与衬底910及其上形成的电路接触。

在一个实施例中,可将压缩压力925施加于衬底910和晶圆950,使得键合层相互压紧。激活后可能处于不稳定的能态,它们之间可能发生反应并形成化学键。因此,介电区域940中的介电材料和介电材料层960可以通过或不经过热处理或压力粘合在一起。

图9D示出在粘合层中的介电材料粘合后粘合粘合层中的触点的退火工艺。例如,触点930和p-触点980或n-触点982可以通过在例如约200-400℃或更高温度下退火粘合在一起。在退火过程中,热935可使触点比介电材料膨胀更多,从而可关闭触点之间的盘状间隙,使得触点垫930与p触点980或n触点982可以接触并可在活化表面形成直接金属键。

在一个实施例中,其中两个键合晶片包括具有不同热膨胀系数的材料,在室温下键合的介电材料可以帮助减少或防止由不同热膨胀引起的接触垫的不对中。在一个实施例中,为了在退火过程中进一步减少或避免接触垫在高温下的不对准,在键合之前,可以在MicroLED之间、MicroLED组之间、通过部分或全部衬底等形成沟槽。

在MicroLED连接到驱动电路后,可以将制造MicroLED的衬底变薄或移除,并且可以在MicroLED的发光表面上制造各种次级光学元件,以提取、准直和重定向从MicroLED的有源区域发射的光。

在一个示例中,可在MicroLED形成微透镜,其中每个微透镜可对应于各自的MicroLED,并且可帮助提高光提取效率并准直由MicroLED发出的光。在一个实施例中,次级光学元件可以在MicroLED的衬底或n型层中制造。次级光学元件可以在沉积在MicroLED的n型侧的介电层中制造。次级光学元件的实例可包括透镜、光栅、增反射(AR)涂层、棱镜、光子晶体等。

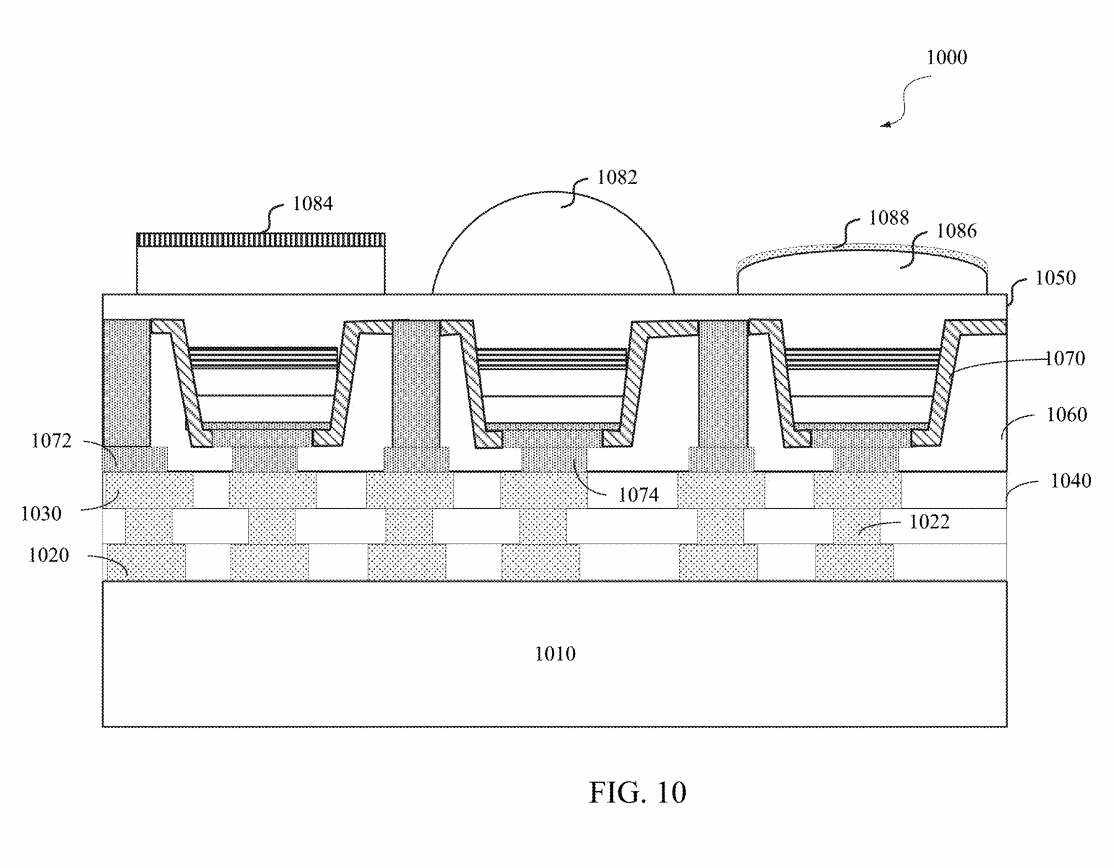

图10示出制造次级光学元件的LED阵列1000的示例。LED阵列1000可以通过使用上述任何合适的键合技术,以将LED芯片或晶圆与包括在其上制造的电路的硅片键合而制成。

在图10所示的示例中,LED阵列1000可以使用如上所述的晶圆对晶圆混合键合技术进行键合。LED阵列1000可以包括衬底1010。可以在衬底1010上制造集成电路1020,例如LED驱动电路。

集成电路1020可通过互连1022和触点1030连接到MicroLED1070的p-触点1074和n-触点1072,其中触点1030可与p-触点1074和n-触点1072形成金属键。衬底1010上的介电层1040可通过熔合键合至介电层1060。

LED芯片或晶圆的衬底(未示出)可以变薄或可以移除以暴露MicroLED1070的n型层1050。可在n型层1050内或其上形成各种次级光学元件,如球面微透镜1082、光栅1084、微透镜1086、增反射层1088等。

例如,球形微透镜阵列可以在MicroLED1070的半导体材料中蚀刻,使用灰度掩模和对曝光光具有线性响应的光刻胶,或使用通过图图化光刻胶层的热回流形成的蚀刻掩模。

同时可以使用类似的光刻技术或其他技术在沉积在n型层1050上的介电层中蚀刻次级光学元件。例如,微透镜阵列可以通过使用二元掩模进行图案化的聚合物层的热回流在聚合物层中形成。

聚合物层中的微透镜阵列可以用作次级光学元件,又可以用作用于将微透镜阵列的轮廓转移到介电层或半导体层中的蚀刻掩模。在一个实施例中,MicroLED1070可具有多个相应的次级光学元件,如微透镜和抗反射涂层、在半导体材料中蚀刻的微透镜和在介电材料层中蚀刻的微透镜、微透镜和光栅、球面透镜和非球面透镜等。

MetaPatent|Micro-LEDdesignforhighlightextractionefficiency

名为“Micro-LEDdesignforhighlightextractionefficiency”的Meta专利申请最初在2022年8月提交,并在日前由美国专利商标局公布。